发布时间:2024-12-23

发布时间:2024-12-23 点击次数:

点击次数: 的关键进步,展现了 Cadence 致力于通过其芯片架构和框架推动行业领先解决方案的承诺。

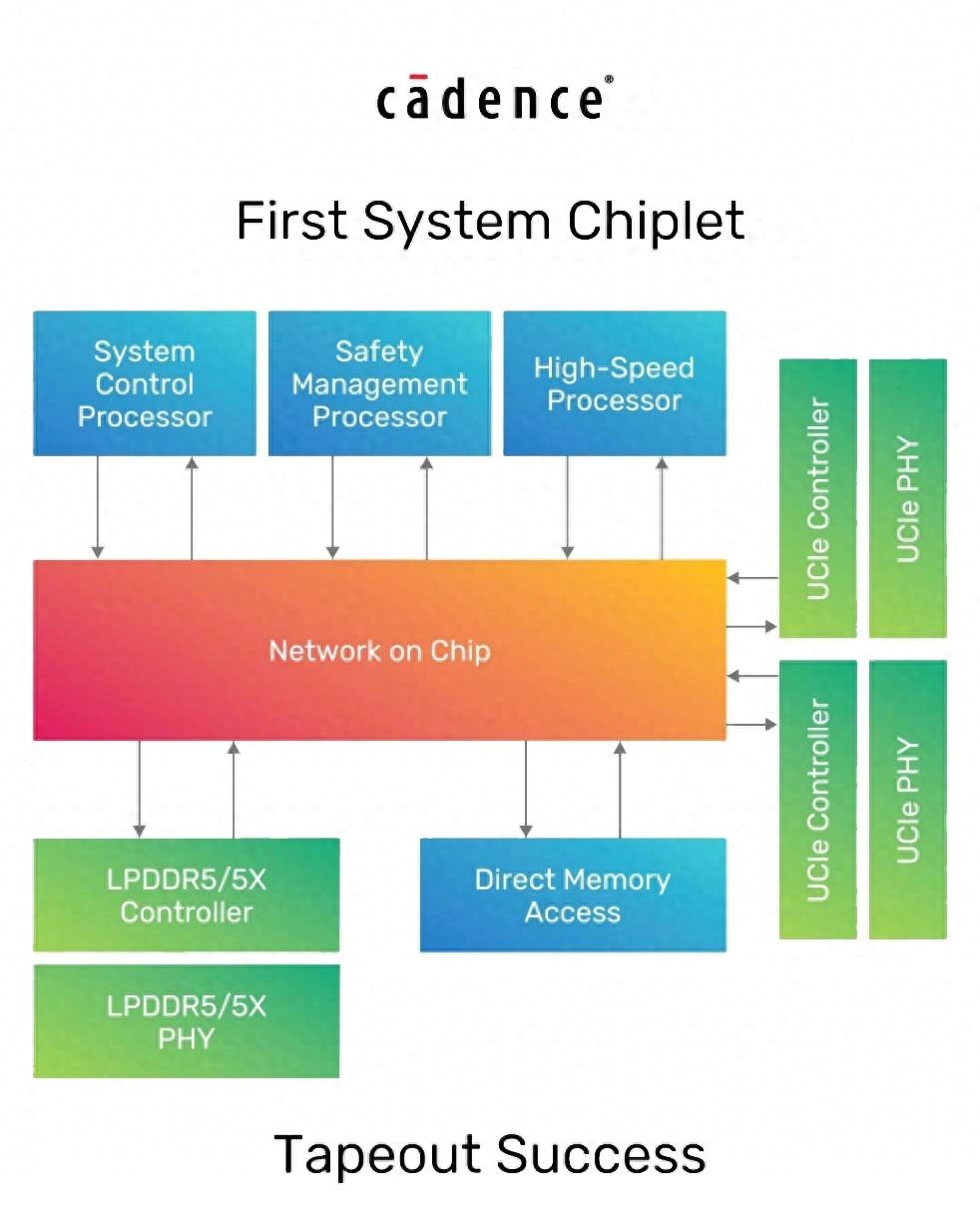

Cadence 成功制作了业界首款系统级小芯片的原型、设计并流片。该芯片将处理器、系统 IP 和内存 IP 集成在一个封装中,通过通用芯片互连标准 (UCIe™)接口进行互连。该芯片与 Arm 共同开发,符合 Arm 的芯片系统架构(CSA),该标准可确保互操作性并加快芯片的上市时间。

2024 年 3 月,Cadence 和 Arm 正式建立长期合作关系,以提供基于芯片的参考设计和尖端软件开发平台。此次合作将 Cadence 强大的 IP 和EDA解决方案与 Arm 先进的 IP 技术相结合,大大降低了设计复杂性并加快了客户的产品上市时间。为进一步的发展奠定了基础,为客户提供了一个全面的开发平台,以实现极佳的性能和效率。

此次合作的核心战略是投资 Arm CSA,从而实现供应商之间更大的组件重用。Cadence 是 CSA 的积极贡献者,正在开发符合此标准的芯片。这些标准允许小芯片(包括 Arm计算子系统(CSS)和 Cadence 系统芯片)实现规模化并加快上市时间。

凭借数十年的 IP 和子系统设计专业知识,硅解决方案事业部可提供高价值解决方案来解决客户挑战。将功能抽象为小芯片 IP 可帮助客户更快地将创新推向市场。Cadence 掌握的先进封装和互连技术可实现可扩展的高性能解决方案,从而提高效率并推动技术进步。

从单片 SoC 转向基于小芯片的设计,其驱动力在于提高设计效率、缩短平台更新周期以及优化功率、性能和面积(PPA)指标。小芯片支持多代工厂业务模式,在同一封装内集成跨代工厂工艺技术。随着技术密度扩展放缓,芯片对于克服摩尔定律限制和工艺掩模版限制至关重要。新的封装和互连解决方案(包括 2.5D 和 3D 封装以及 UCIe 等芯片到芯片接口)支持这种变革性方法,为客户提供了加速创新和市场准备的途径。

Cadence 在小芯片技术方面的开创性工作代表了半导体行业的重大进步。Cadence 通过创新的架构、强大的 IP 和战略合作伙伴关系,为效率、可扩展性和性能树立了新的标杆。这些发展满足了高性能计算、汽车和数据中心行业不断变化的需求,并帮助客户克服设计挑战并加快产品上市时间。Cadence 始终致力于突破技术界限,塑造小芯片生态系统的未来。

、三星晶圆代工厂 (Samsung Foundry)、ADTechnology 和 Rebellions 正在联手向市场

联盟 /

、宝马、博世、SiliconAuto、西门子和Valeo等欧洲企业,以及ASE、

对 PCIe 技术的坚定承诺和支持,在业界有AG真人国际目共睹。我们深知强大 PCIe 生态

的重要性,并感谢 PCI-SIG 提供的平台。在 PCI-SIG 开发者大会迎来 32 周年之际,

展示完整的PCIe 7.0 IP解决方案 /

Janus Network-on-Chip(NoC)。 随着当今计算需求的不断提高

(CSS),提供领先的人工智能体验 /

公司合作,提供基于芯粒的参考设计和软件开发平台,以加速软件定义汽车(SDV)取得创新。

)宣布与BETA CAE Systems International AG达成收购协议。BETA CAE作为全球领先的多领域工程仿真解决方案供应商,其卓越的

横向或纵向组装成先进的SiP(system-in- package)形式。

是否也走上了集成竞赛的道路? /

® Millennium™ Enterprise Multiphysics Platform,这是一款面向多

技术是一种在半导体设计和制造中将大型芯片的不同功能分解并分散实现在多个较小和专用的芯片(Chiplets)上的方法。这些较小的芯片随后通过高速互连方式集成到一个封装中,共同实现全功能的芯片

技术? /

一套新的应用,可显著增强旗舰产品 Palladium Z2 Enterprise Emulation System 的功能

照不同的计算单元或功能单元对其进行分解,然后每个单元选择最适合的工艺制程进行制造,再将这些模块化的裸片互联起来,降低芯片设计的成本和难度。

模型已经被证明是可行的,目前AMD、英特尔、博通和Marvell等公司都已经

技术是一种将集成电路设计和制造的方法,其中一个芯片被分割成多个较小的独立单元,这些单元通常被称为“chiplets”。每个

Zephyr领进门系列:MCUXPresso for VS Code插件安装

飞凌嵌入式ElfBoard ELF 1板卡-mfgtools烧录流程之烧写方法

【正点原子STM32H7R3开发套件试用体验】4G联网工业设备控制网关